AI-POWERED DOCS

What do you want to know?

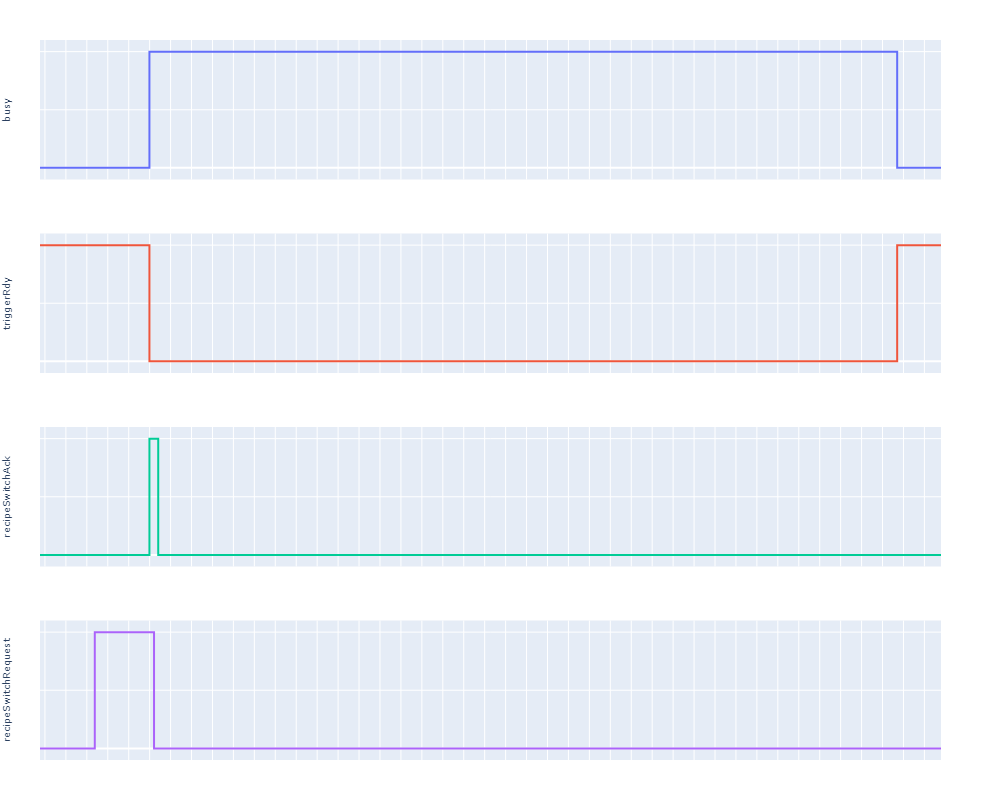

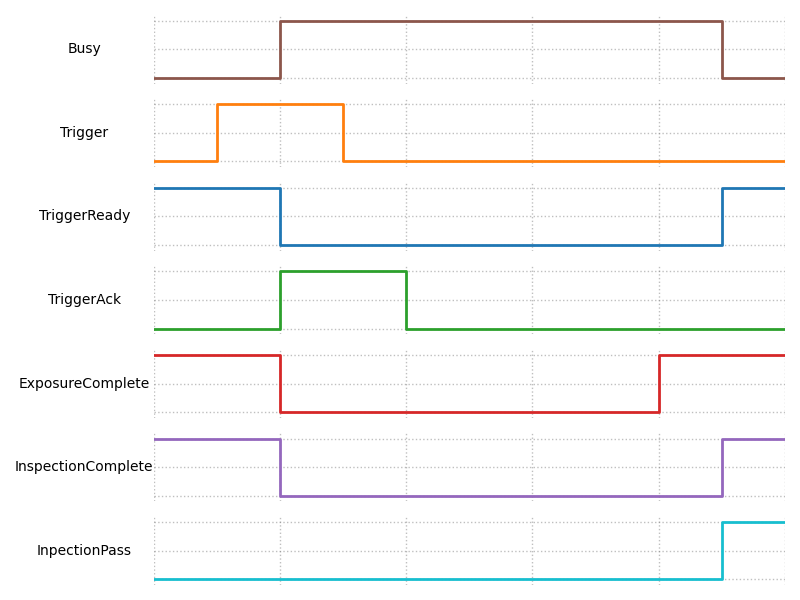

I/O Timing Diagrams

Trang này trình bày chi tiết các thông số kỹ thuật về thời gian cho digital I/O của OV20i, bao gồm thời gian tín hiệu trigger, độ trễ đầu ra và độ rộng xung được khuyến nghị.

Digital Input Timing

Trigger Input Timing (Pin 16)

| Tham Số | Thông Số Kỹ Thuật |

|---|---|

| Loại Kích Hoạt Đầu Vào | NPN (Pull to GND) |

| Độ Rộng Xung Tối Thiểu | 10 ms |

| Input Debounce | ~5 ms |

| Tần Số Đầu Vào Tối Đa | ~20 Hz |

| Loại Tín Hiệu | Dry contact hoặc open collector |

Trigger kích hoạt một lần cho mỗi xung

Phù hợp cho các cảm biến có tín hiệu chuyển đổi đầu ra ổn định

Digital Output Timing

Result Output Timing (Pins 10 & 11)

| Sự Kiện | Thời Gian |

|---|---|

| Độ Trễ Kích Hoạt Đầu Ra | ~10–15 ms sau khi inference |

| Thời Gian Đầu Ra Hoạt Động | Có thể cấu hình (mặc định 100 ms) |

| Dòng Điện Tối Đa | 100 mA |

| Loại Logic Đầu Ra | NPN open collector (pulls to GND) |

cảnh báo

Digital outputs là loại NPN open-collector, chỉ sinking. Chúng kéo đường tín hiệu xuống GND khi được kích hoạt và không thể cấp nguồn +24 V. Cần cung cấp điện trở pull-up hoặc tải ngoài đến +24 V để hoạt động đúng.

Chuỗi Thời Gian Điển Hình (Digital Trigger)

CopyEdit

Trigger Pulse

___

| |____________________

|

|<-- 10 ms -->|

Inference Timing (AI Process)

_______________________

/

Result Output __/

|<-- ~10–15 ms after trigger -->|

Thiết Lập Được Khuyến Nghị

- Trigger qua dry contact, cảm biến NPN, hoặc đầu ra sinking của PLC

- Đặt độ rộng xung tối thiểu: 10–20 ms

- Cấu hình thời gian đầu ra qua giao diện UI hoặc tag PLC nếu cần

Thực Hành Tốt Nhất

- Sử dụng cáp có vỏ chống nhiễu để giảm thiểu nhiễu

- Xác nhận hành vi cạnh lên/xuống (rising/falling edge) khớp với yêu cầu của PLC

- Kiểm tra đầu ra bằng đèn thử hoặc đồng hồ đa năng trong quá trình thiết lập

- Tránh hiện tượng nhiễu tín hiệu (signal bounce) bằng cách sử dụng cảm biến có tích hợp debounce